Verilogの勉強もかねてCPLDで時計を作ってみようと思います。

Verilog - Wikipedia

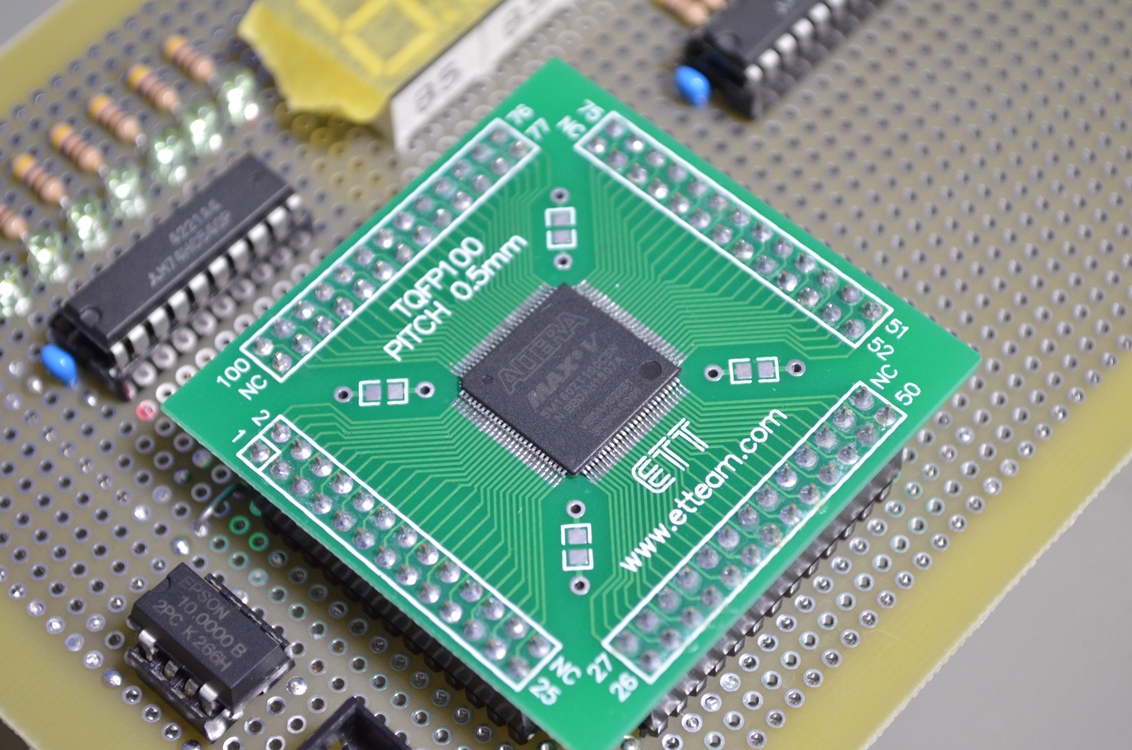

CPLDはMAX Vファミリの「5M160ZT100C5N 」というものを使ってみました。

このCPLDはdigikeyなどで比較的安く手に入れることができます。

(ゲート数によるけども200~500円程度)

Just a moment...

制御が簡単なので7seg 6桁として1秒単位で表示できるようにしてみました。

IOポートが79本もあるのでデバック用のLEDなんかもついています。

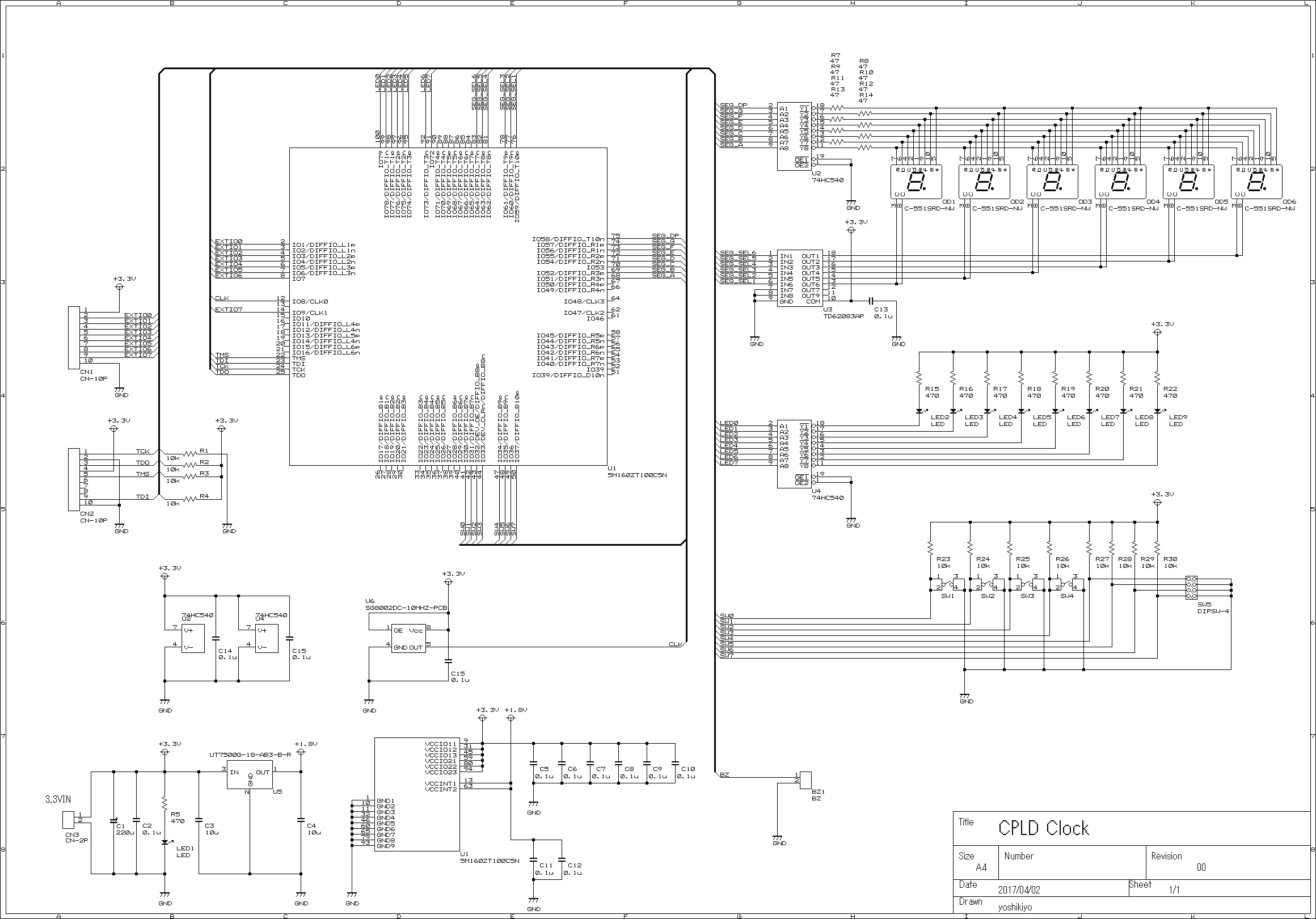

回路図

とりあえず動作確認としてLチカまではOK

ソースコード

//*****************************************************************************

// LED点滅1

// LEDを点滅させる

//*****************************************************************************

module CPLDTop(

input wire CLK,

output wire[7:0]LED

);

reg [24:0] count;

reg T1s;

reg toggle;

//--------------------------------------------

//10MHzクロックから1Hzを生成

//--------------------------------------------

always@(posedge CLK) begin

if(count == 24'd9999999) begin

count <= 24'd0;

T1s <= 1'b1;

end

else begin

count <= count + 24'd1;

T1s <= 1'b0;

end

end

//--------------------------------------------

//1秒おきにtoggleする

//--------------------------------------------

always@(posedge T1s) begin

toggle <= ~toggle;

end

//--------------------------------------------

//LEDに接続

//--------------------------------------------

assign LED[7] = toggle;

assign LED[6] = toggle;

assign LED[5] = toggle;

assign LED[4] = toggle;

assign LED[3] = toggle;

assign LED[2] = toggle;

assign LED[1] = toggle;

assign LED[0] = toggle;

endmodule//*****************************************************************************

// LED点滅2

// LEDを順番に点灯させる

//*****************************************************************************

module CPLDTop(

input wire CLK,

output wire[7:0]LED

);

reg [23:0] count;

reg [2:0] T1s;

//--------------------------------------------

//10MHzクロックから1Hzを生成

//1秒ごとに3bitカウンタをカウントアップ

//--------------------------------------------

always@(posedge CLK) begin

if(count == 24'd9999999) begin

count <= 24'd0;

if(T1s == 3'd7) begin

T1s <= 3'd0;

end

else begin

T1s <= T1s + 3'd1;

end

end

else begin

count <= count + 24'd1;

//T1s <= 1'b0;

end

end

//--------------------------------------------

//3 to 8デコーダ

//--------------------------------------------

function [7:0] DEC (

input [2:0] DECIN

);

begin

case (DECIN)

3'h7 : DEC = 8'b1000_0000;

3'h6 : DEC = 8'b0100_0000;

3'h5 : DEC = 8'b0010_0000;

3'h4 : DEC = 8'b0001_0000;

3'h3 : DEC = 8'b0000_1000;

3'h2 : DEC = 8'b0000_0100;

3'h1 : DEC = 8'b0000_0010;

3'h0 : DEC = 8'b0000_0001;

default : DEC = 8'bx;

endcase

end

endfunction

//--------------------------------------------

//デコーダの出力をLEDに接続

//--------------------------------------------

assign LED[7:0] = DEC(T1s);

endmodule

コメント